The work package "Demonstrators” is the proof of the APECS project. Unlike most projects, the demonstrators are not intended to evaluate a developed process or a built equipment. In APECS, the demonstrators are used to check the conceived production chain regarding possible gaps, but in particular also the interfaces at material and data level between all stations. The aim is not only to optimize the transfer to the next work step, but also to ensure that information flows into the previous steps in order to work efficiently and optimally.

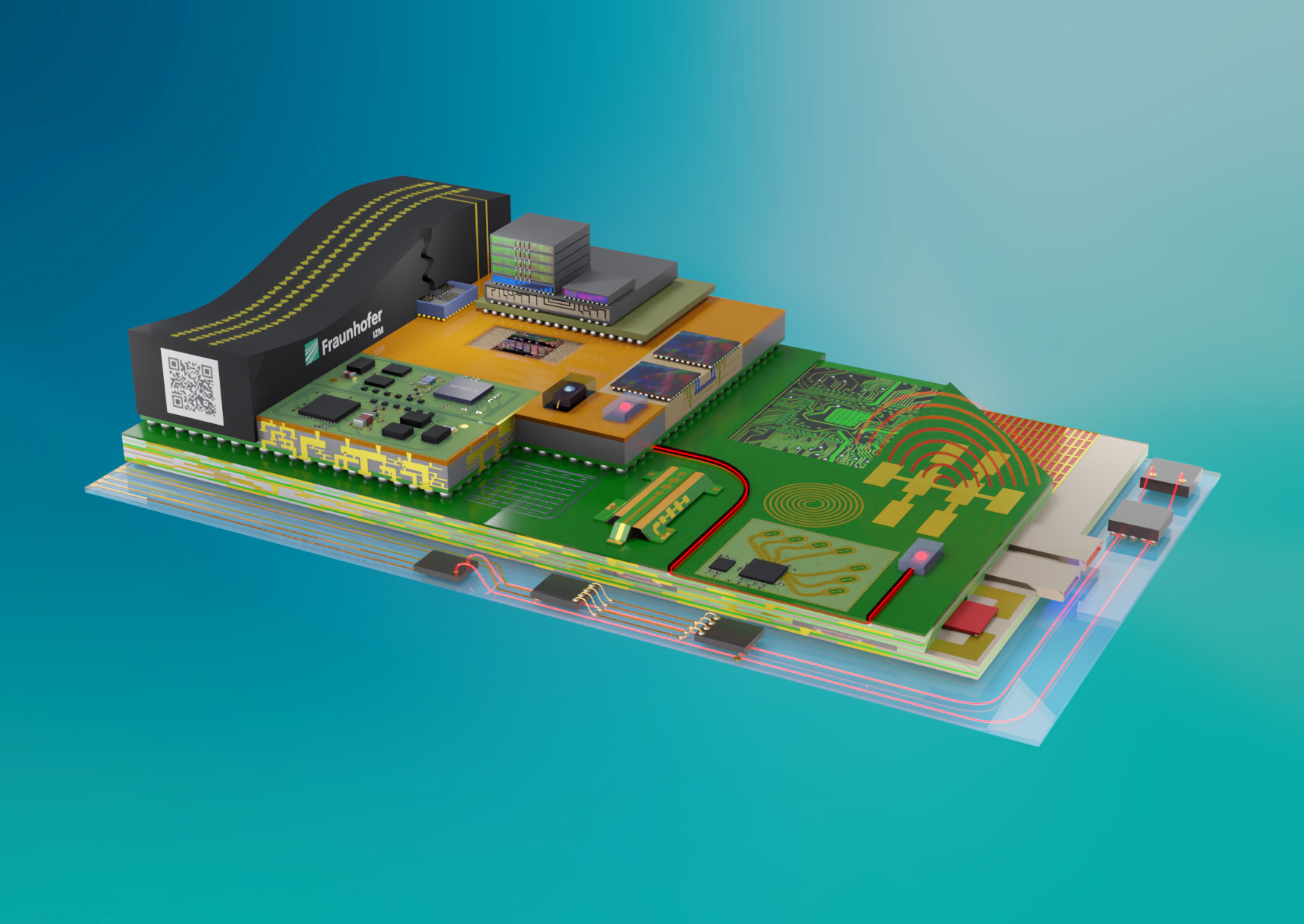

The demonstrators were chosen to address all current and foreseeable challenges in microelectronics. All demonstrators are chiplets or chiplet modules.

The HPC (High Performance Computing) demonstrator will not only prove the chiplet approach for computers of all kinds, including analog computers, but will also evaluate the feasibility of the STCO (system-technology co-optimization) approach. In this comprehensive design approach, the system requirements are incorporated directly into the design of chips and chiplets, which are then manufactured optimally using appropriately adapted technology. The weighting of the criteria (cost, size, energy consumption, etc.) is then determined by the customer.

The multi-material sensor demonstrator shows the high modularity of the chiplets. In addition to central tasks such as the driver unit, readout unit, and evaluation unit, a wide variety of sensors can be integrated with additional chiplets. These can be simple temperature or magnetic field sensors, but also complex chiplets such as LiDAR, gas sensors, or acoustic systems. The challenge lies not only in reliably combining materials with different coefficients of expansion in a very small space, but also in the risk of unwanted mutual interference between the various physical measurement methods.

The chiplets from the radio frequency range are so diverse that they cannot be reproduced in a demonstrator. Therefore, various chiplets are being developed that address both data communication and radar applications. Noteworthy here are the approaches with fanout wafer-level packaging and the only chiplet with a flexible carrier.

APECS – European pilot line for advanced packaging and heterogeneous integration

APECS – European pilot line for advanced packaging and heterogeneous integration