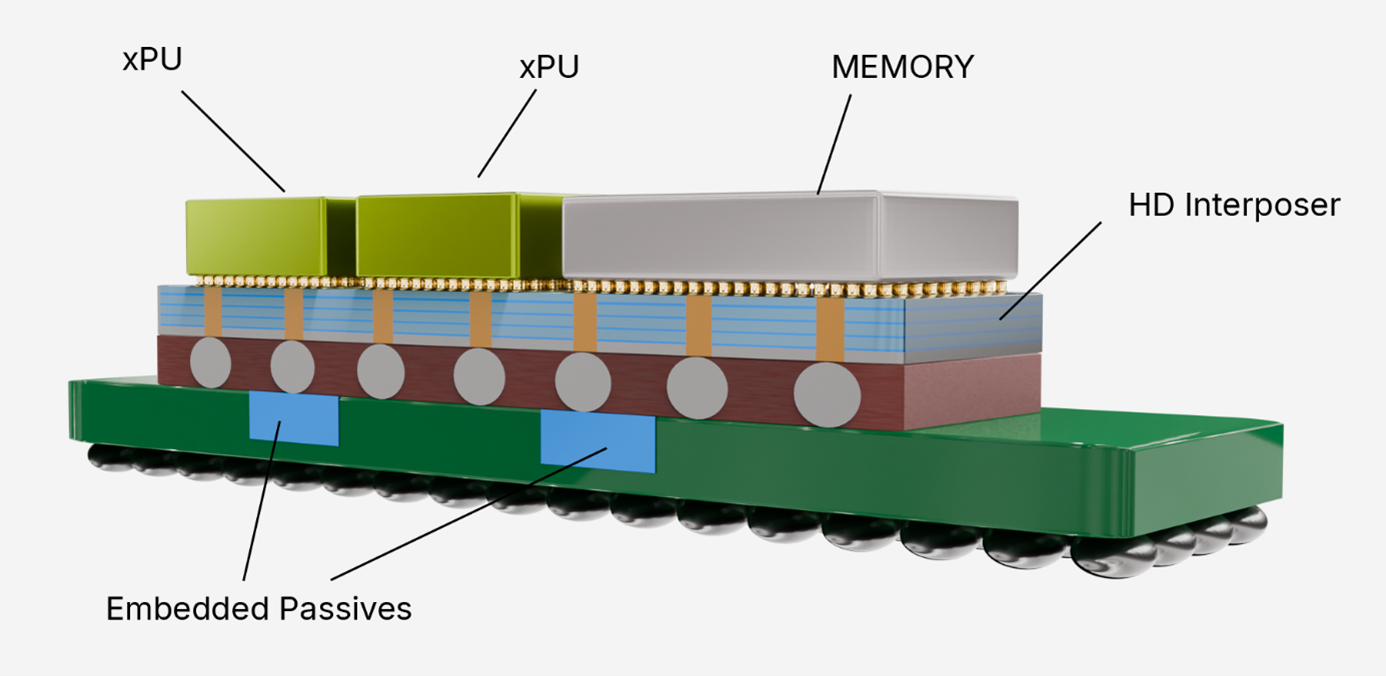

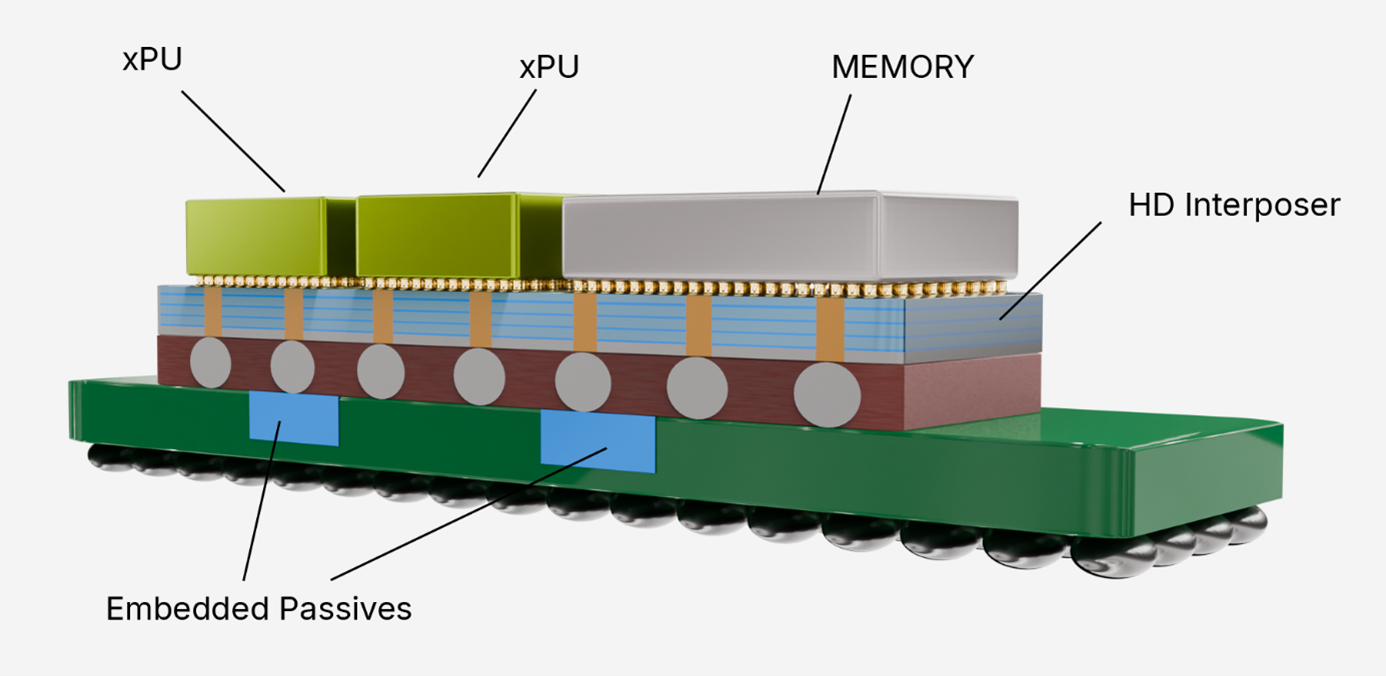

High performance computing (HPC) chiplet

Target

While the other demos provide special tailored solutions for special needs the functional demonstrator 6.1.1 will set an example of a more versatile heterogenous integration that is currently available for chiplets that are to be designed now using technologies that are already available and affordable.

Moreover, there are demonstrator structures and assemblies in T 6.1.2 that show how the technological capabilities of the pilot line will extend along the timeline and enable characterization of the new capabilities for the System-Technology-Co-Optimization.

Innovations

The demonstrators will help to find a common language and better communication between the worlds of system and technology to provide the technology to a wider audience.

There will be the manufacturing of ultra-high-density redistribution layers and through silicon vias. Also, resistors and capacitors will be embedded into the silicon interposers. The work package will furthermore improve assembly on advanced organic substrate.

Partners

The AISEC will supply Security IP and test for security issues. IIS will supply the design of the chiplets and the system of the functional demonstrator. IIS-EAS will support the system design and execute the STCO. IMWS will supply fault detection for the manufactured assemblies. IPMS-CNT will implement the passives on silicon interposer. IZM will care for fine-line high speed data lines, die-assembly, encapsulation and board mounting. IZM-ASSID will bring their 300 mm wafer level interposer-Technologies.

Impact

Led by the example assemblies customers can select the parts they need for the integration of their products to have an easy entry into the topic of heterogeneous integration which will be new for many chiplet designers. The characterization of the new capabilities will outcome into data that is needed to incorporate the new capabilities into the design considerations and the STCO.

APECS – European pilot line for advanced packaging and heterogeneous integration

APECS – European pilot line for advanced packaging and heterogeneous integration