Target:

The demands placed on modern electronic systems are constantly growing: ever smaller designs, increasing performance requirements, lower energy consumption, and high reliability throughout the entire life cycle. Wafer-level packaging (WLP) offers answers to many of these challenges – and Fraunhofer is one of the world's leading institutes for research and development in this field.

Impact:

Fraunhofer sees itself as a link between research and application. In addition to developing innovative processes, the institute supports the industry in different ways:

- Pilot line production and advanced prototyping utilizing in-house clean room

- Support with design, layout, and simulation

- Training, technology consulting, and IP transfer

Innovations:

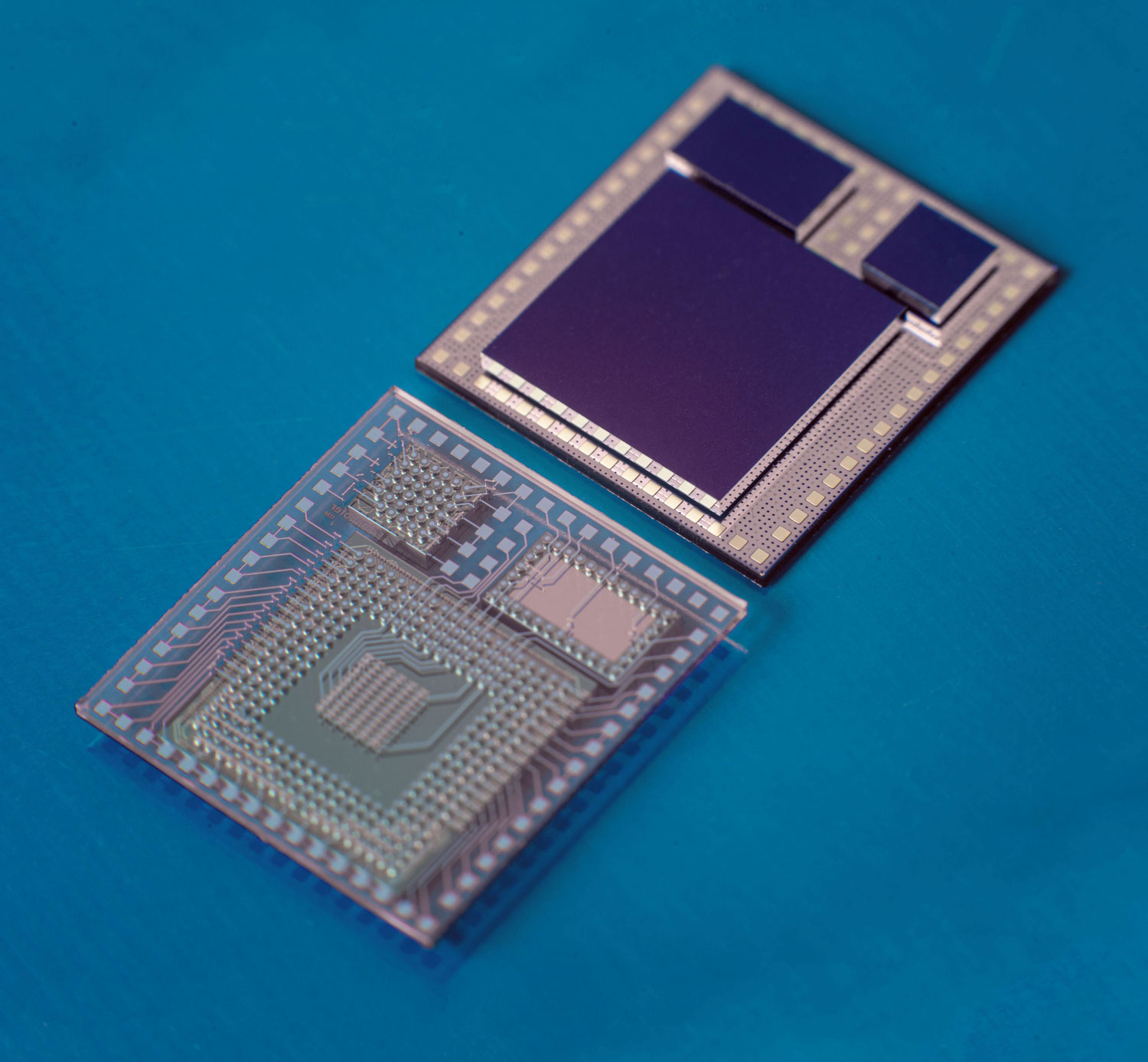

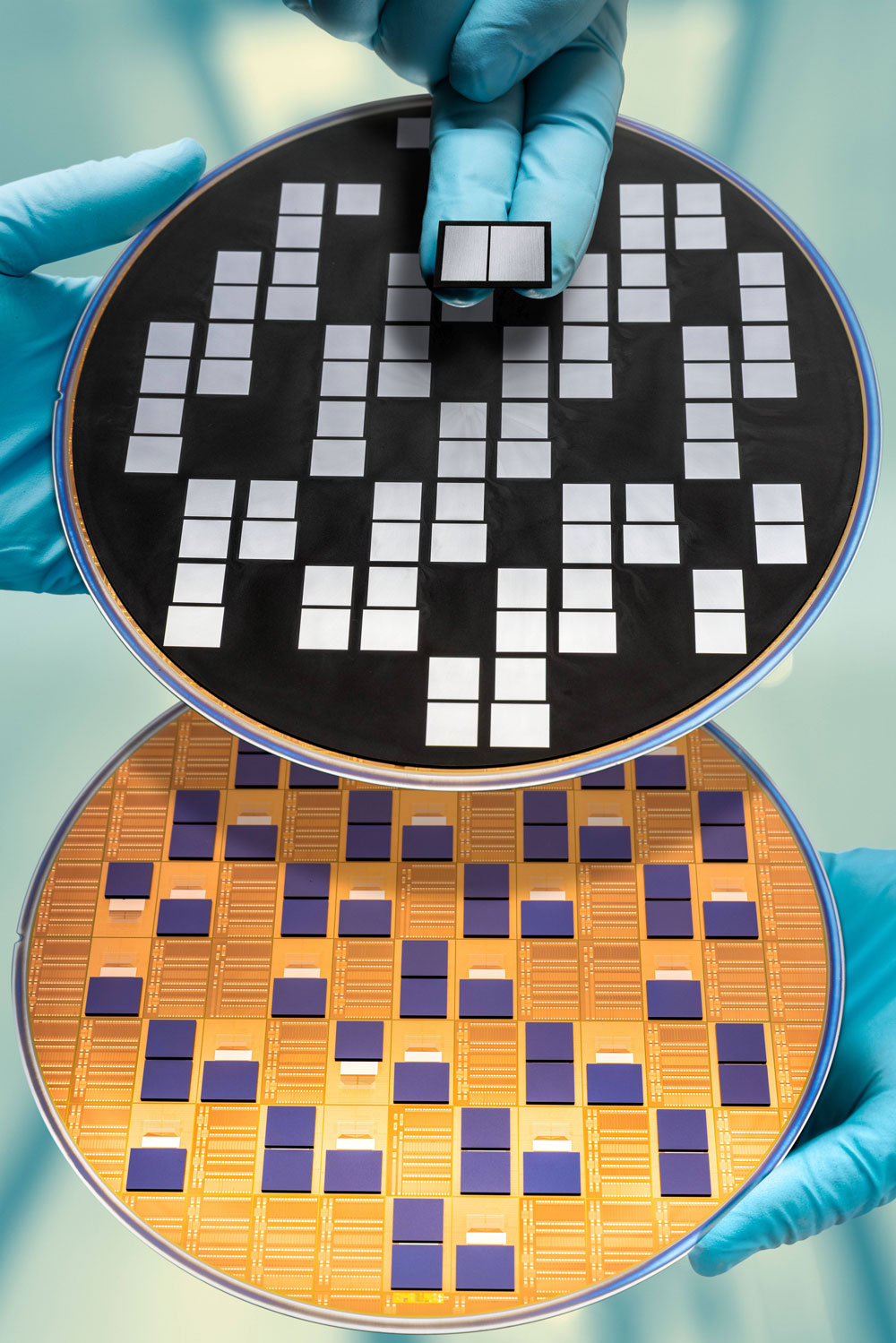

Fan-in and fan-out wafer-level packaging (WLP)

Fan-in WLP is the classic form of WLP, in which the redistribution layer (RDL) is located within the original chip area. This method is particularly suitable for components with a low to medium number of connections – e.g., in mobile devices or sensor applications.

Fan-out WLP (FOWLP), on the other hand, allows the contact areas to be placed outside the original chip area by first embedding the chip in a carrier material and then redistributing it. This allows significantly higher I/O densities and is particularly interesting for complex high-performance applications.

- Process development for FOWLP, including chip embedding and RDL

- Multi-die fan-out packaging (e.g., heterogeneous integration of logic + memory)

- Ultra-thin packages for high-density applications

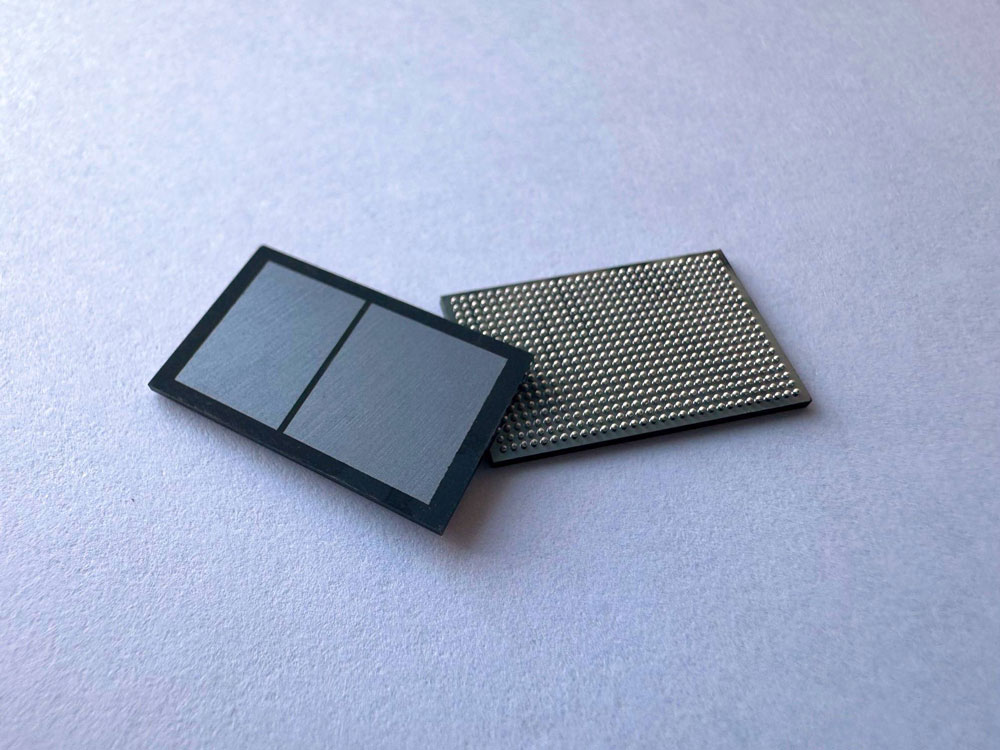

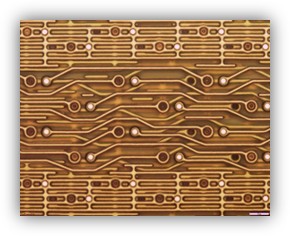

Redistribution layer (RDL)

The redistribution layer is a core component of every WLP solution. It relocates the electrical contacts from the original pad layout to a new, adapted grid – for example, in preparation for bumping or for connection to other substrates.

- Development of thin, multilayer RDL structures at wafer-level

- Use of innovative materials such as thin, low-temperature PI dielectrics

- Fine-pitch layouts down to <5 µm line/spacing with high manufacturing yield

- Combination with through-silicon vias (TSVs) for vertical connections

- Fine-pitch and ultra-fine pitch bump interconnects with a wide variety of bumping metals like Cu/Sn(Ag), Cu/Sn, Ni/Au, Au, AuSn, nano-porous Au (NPG), In, InSn tailored for specific applications

APECS – European pilot line for advanced packaging and heterogeneous integration

APECS – European pilot line for advanced packaging and heterogeneous integration